Read input only on edge of clock cycle positive or negative example below.

Edge triggered t flip flop truth table.

Below we have described the various states of t flip flop using a breadboard circuit with icmc74hc73a.

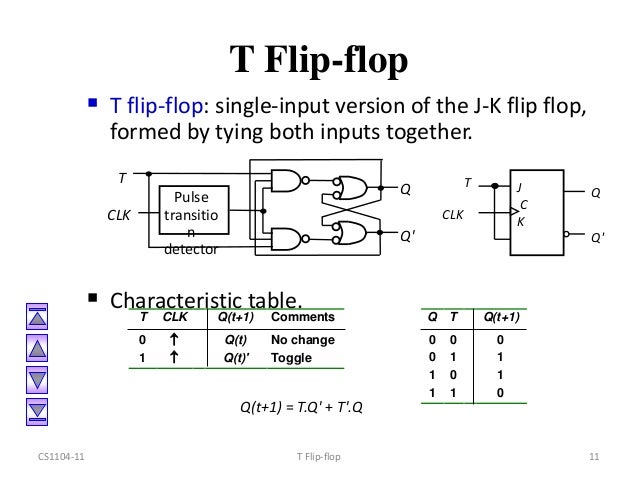

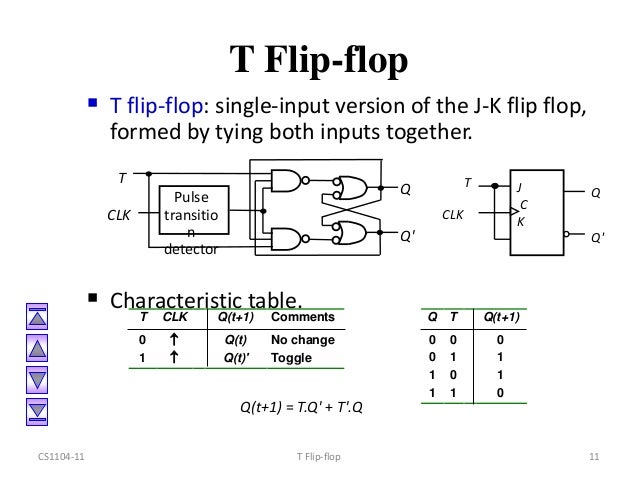

These are basically a single input version of jk flip flop.

Truth table of t flip flop.

This modified form of jk flip flop is obtained by connecting both inputs j and k together.

In negative edge triggered flip flops the clock samples the input lines at the negative edge falling edge or trailing edge of the clock pulse.

T flip flop.

A demonstration video is also given below.

If the output q 0 then the upper nand is in enable state and lower nand gate is in disable condition.

The output of the flip flop is set or reset at the negative edge of the clock pulse.

The first electronic flip flop was invented in 1918 by the british physicists william eccles and f.

Since the clock is high to low edge triggered both input button should be pressed and hold till releasing the clock button.

The design was used in the 1943 british colossus codebreaking computer and such circuits and their transistorized versions were common in computers even after the.

The only difference between them is in jk flip flop indeterminate state does not occur.

The operation and truth table for a negative edge triggered flip flop are the same as those for a positive except that the falling edge of the clock pulse is the triggering edge.

Sr flip flop vs jk flip flop both jk flip flop and sr flip flop are functionally same.

It stands for set reset flip flop.

This flip flop has only one input along with the clock input.

A symbolic representation of negative edge triggering has been shown in figure 3.

In other words the present state gets inverted when both the inputs are 1.

Construction of sr flip flop there are following two methods for constructing a sr flip flop by using nor latch.

It was initially called the eccles jordan trigger circuit and consisted of two active elements vacuum tubes.

A t flip flop is like jk flip flop.

As mentioned earlier t flip flop is an edge triggered device.

Only the value of d at the positive edge matters.

The basic operation is illustrated below along with the truth table for this type of flip flop.

Truth table of d flip flop.

A small circle is put before the.

For example consider a t flip flop made of nand sr latch as shown below.

In this article we will discuss about sr flip flop.

The truth table of a t flip flop is shown below.

In jk flip flop instead of indeterminate state the present state toggles.

Sr flip flop sr flip flop is the simplest type of flip flops.

D c s c r d clock q q.

Positive edge triggered d flip flop on the positive edge while the clock is going from 0 to 1 the input d is read and almost immediately propagated to the output q.

Thus d flip flop is a controlled bi stable latch where the clock signal is the control signal.

It is a clocked flip flop.

Thus the output has two stable states based on the inputs which have been discussed below.